# **Chipyard Documentation**

**Berkeley Architecture Research**

Jan 20, 2021

# Contents

| 1 | Getti | Getting Help      |                                                        |   |  |  |  |

|---|-------|-------------------|--------------------------------------------------------|---|--|--|--|

| 2 | Table | Table of Contents |                                                        |   |  |  |  |

|   | 2.1   | Chipya            | rd Basics                                              |   |  |  |  |

|   |       | 2.1.1             | Chipyard Components                                    | : |  |  |  |

|   |       | 2.1.2             | Development Ecosystem                                  |   |  |  |  |

|   |       | 2.1.3             | Configs, Parameters, Mixins, and Everything In Between | ; |  |  |  |

|   |       | 2.1.4             | Initial Repository Setup                               | 1 |  |  |  |

|   | 2.2   | Simulat           | tion                                                   | 1 |  |  |  |

|   |       | 2.2.1             | Software RTL Simulation                                | 1 |  |  |  |

|   |       | 2.2.2             | FPGA-Accelerated Simulation                            | 1 |  |  |  |

|   | 2.3   | Include           | d RTL Generators                                       | 1 |  |  |  |

|   |       | 2.3.1             | Rocket Chip                                            | 1 |  |  |  |

|   |       | 2.3.2             | Rocket Core                                            | 2 |  |  |  |

|   |       | 2.3.3             | Berkeley Out-of-Order Machine (BOOM)                   | 2 |  |  |  |

|   |       | 2.3.4             | Hwacha                                                 | 2 |  |  |  |

|   |       | 2.3.5             | Gemmini                                                | 2 |  |  |  |

|   |       | 2.3.6             | IceNet                                                 | 2 |  |  |  |

|   |       | 2.3.7             | Test Chip IP                                           | 2 |  |  |  |

|   |       | 2.3.8             | SiFive Generators                                      | 3 |  |  |  |

|   |       | 2.3.9             | SHA3 RoCC Accelerator                                  | 3 |  |  |  |

|   |       | 2.3.10            | CVA6 Core                                              | 3 |  |  |  |

|   |       | 2.3.11            | NVDLA                                                  | 3 |  |  |  |

|   |       | 2.3.12            | Sodor Core                                             | 3 |  |  |  |

|   | 2.4   | Develop           | pment Tools                                            | 3 |  |  |  |

|   |       | 2.4.1             | Chisel                                                 | 3 |  |  |  |

|   |       | 2.4.2             | FIRRTL                                                 | 3 |  |  |  |

|   |       | 2.4.3             | Treadle and FIRRTL Interpreter                         | 3 |  |  |  |

|   |       | 2.4.4             | Chisel Testers                                         | 3 |  |  |  |

|   |       | 2.4.5             | Dsptools                                               | 3 |  |  |  |

|   |       | 2.4.6             | Barstools                                              | 3 |  |  |  |

|   |       | 2.4.7             | Dromajo                                                | 3 |  |  |  |

|   | 2.5   | VLSI F            | 'low                                                   | 3 |  |  |  |

|   |       | 2.5.1             | Building A Chip                                        | 3 |  |  |  |

|   |       | 2.5.2             | Core Hammer                                            | 3 |  |  |  |

|   |       | 2.5.3             | Configuration (Hammer IR)                              | 4 |  |  |  |

|   |       | 2.0.0             |                                                        |   |  |  |  |

|      | 2.5.4  | Tool Plugins         40                                               |

|------|--------|-----------------------------------------------------------------------|

|      | 2.5.5  | Technology Plugins         41                                         |

|      | 2.5.6  | Using Hammer To Place and Route a Custom Block                        |

|      | 2.5.7  | ASAP7 Tutorial                                                        |

|      | 2.5.8  | Advanced Usage                                                        |

| 2.6  | Custom | ization                                                               |

|      | 2.6.1  | Heterogeneous SoCs                                                    |

|      | 2.6.2  | Integrating Custom Chisel Projects into the Generator Build System 54 |

|      | 2.6.3  | Adding a custom core                                                  |

|      | 2.6.4  | RoCC vs MMIO                                                          |

|      | 2.6.5  | Adding a RoCC Accelerator                                             |

|      | 2.6.6  | MMIO Peripherals                                                      |

|      | 2.6.7  | Dsptools Blocks                                                       |

|      | 2.6.8  | Keys, Traits, and Configs                                             |

|      | 2.6.9  | Adding a DMA Device         79                                        |

|      | 2.6.10 | Incorporating Verilog Blocks                                          |

|      | 2.6.11 | Memory Hierarchy                                                      |

|      | 2.6.12 | Chipyard Boot Process                                                 |

|      | 2.6.13 | Adding a Firrtl Transform    88                                       |

|      | 2.6.14 | IOBinders and HarnessBinders    90                                    |

| 2.7  | 0      | Software                                                              |

|      | 2.7.1  | FireMarshal                                                           |

|      | 2.7.2  | The RISC-V ISA Simulator (Spike)    92                                |

|      | 2.7.3  | Baremetal RISC-V Programs                                             |

| 2.8  |        | ed Concepts                                                           |

|      | 2.8.1  | Tops, Test-Harnesses, and the Test-Driver93                           |

|      | 2.8.2  | Communicating with the DUT                                            |

|      | 2.8.3  | Debugging RTL                                                         |

|      | 2.8.4  | Debugging BOOM 100                                                    |

|      | 2.8.5  | Accessing Scala Resources                                             |

|      | 2.8.6  | Context-Dependent-Environments                                        |

| 2.9  |        | k and Diplomacy Reference                                             |

|      | 2.9.1  | TileLink Node Types    104                                            |

|      | 2.9.2  | Diplomacy Connectors                                                  |

|      | 2.9.3  | TileLink Edge Object Methods    109                                   |

|      | 2.9.4  | Register Router         113                                           |

|      | 2.9.5  | Diplomatic Widgets                                                    |

| 2.10 | • •    | ping Flow                                                             |

|      | 2.10.1 | General Setup and Usage                                               |

|      | 2.10.2 | Running a Design on VCU118                                            |

|      | 2.10.3 | Running a Design on Arty 127                                          |

|      |        |                                                                       |

## 3 Indices and tables

Chipyard is a framework for designing and evaluating full-system hardware using agile teams. It is composed of a collection of tools and libraries designed to provide an integration between open-source and commercial tools for the development of systems-on-chip.

Important: New to Chipyard? Jump to the Initial Repository Setup page for setup instructions.

# CHAPTER 1

# Getting Help

If you have a question about Chipyard that isn't answered by the existing documentation, feel free to ask for help on the Chipyard Google Group.

# CHAPTER 2

# Table of Contents

## 2.1 Chipyard Basics

These sections will walk you through the basics of the Chipyard framework:

- First, we will go over the components of the framework.

- Next, we will go over how to understand how Chipyard configures its designs.

- Then, we will go over initial framework setup.

Hit next to get started!

## 2.1.1 Chipyard Components

#### Generators

The Chipyard Framework currently consists of the following RTL generators:

## **Processor Cores**

Rocket Core An in-order RISC-V core. See Rocket Core for more information.

- **BOOM** (Berkeley Out-of-Order Machine) An out-of-order RISC-V core. See *Berkeley Out-of-Order Machine* (*BOOM*) for more information.

- CVA6 Core An in-order RISC-V core written in System Verilog. Previously called Ariane. See CVA6 Core for more information.

## Accelerators

- **Hwacha** A decoupled vector architecture co-processor. Hwacha currently implements a non-standard RISC-V extension, using a vector architecture programming model. Hwacha integrates with a Rocket or BOOM core using the RoCC (Rocket Custom Co-processor) interface. See *Hwacha* for more information.

- Gemmini A matrix-multiply accelerator targeting neural-networks

- **SHA3** A fixed-function accelerator for the SHA3 hash function. This simple accelerator is used as a demonstration for some of the Chipyard integration flows using the RoCC interface.

## System Components:

icenet A Network Interface Controller (NIC) designed to achieve up to 200 Gbps.

**sifive-blocks** System components implemented by SiFive and used by SiFive projects, designed to be integrated with the Rocket Chip generator. These system and peripheral components include UART, SPI, JTAG, I2C, PWM, and other peripheral and interface devices.

AWL (Analog Widget Library) Digital components required for integration with high speed serial links.

testchipip A collection of utilities used for testing chips and interfacing them with larger test environments.

## Tools

- **Chisel** A hardware description library embedded in Scala. Chisel is used to write RTL generators using metaprogramming, by embedding hardware generation primitives in the Scala programming language. The Chisel compiler elaborates the generator into a FIRRTL output. See *Chisel* for more information.

- **FIRRTL** An intermediate representation library for RTL description of digital designs. FIRRTL is used as a formalized digital circuit representation between Chisel and Verilog. FIRRTL enables digital circuits manipulation between Chisel elaboration and Verilog generation. See *FIRRTL* for more information.

- **Barstools** A collection of common FIRRTL transformations used to manipulate a digital circuit without changing the generator source RTL. See *Barstools* for more information.

- **Dsptools** A Chisel library for writing custom signal processing hardware, as well as integrating custom signal processing hardware into an SoC (especially a Rocket-based SoC).

- **Dromajo** A RV64GC emulator primarily used for co-simulation and was originally developed by Esperanto Technologies. See *Dromajo* for more information.

## **Toolchains**

- **riscv-tools** A collection of software toolchains used to develop and execute software on the RISC-V ISA. The include compiler and assembler toolchains, functional ISA simulator (spike), the Berkeley Boot Loader (BBL) and proxy kernel. The riscv-tools repository was previously required to run any RISC-V software, however, many of the riscv-tools components have since been upstreamed to their respective open-source projects (Linux, GNU, etc.). Nevertheless, for consistent versioning, as well as software design flexibility for custom hardware, we include the riscv-tools repository and installation in the Chipyard framework.

- **esp-tools** A fork of riscv-tools, designed to work with the Hwacha non-standard RISC-V extension. This fork can also be used as an example demonstrating how to add additional RoCC accelerators to the ISA-level simulation (Spike) and the higher-level software toolchain (GNU binutils, riscv-opcodes, etc.)

## Software

**FireMarshal** FireMarshal is the default workload generation tool that Chipyard uses to create software to run on its platforms. See *FireMarshal* for more information.

## Sims

- **Verilator** Verilator is an open source Verilog simulator. The verilator directory provides wrappers which construct Verilator-based simulators from relevant generated RTL, allowing for execution of test RISC-V programs on the simulator (including vcd waveform files). See *Verilator (Open-Source)* for more information.

- VCS VCS is a proprietary Verilog simulator. Assuming the user has valid VCS licenses and installations, the vcs directory provides wrappers which construct VCS-based simulators from relevant generated RTL, allowing for execution of test RISC-V programs on the simulator (including vcd/vpd waveform files). See *Synopsys VCS* (*License Required*) for more information.

- **FireSim** FireSim is an open-source FPGA-accelerated simulation platform, using Amazon Web Services (AWS) EC2 F1 instances on the public cloud. FireSim automatically transforms and instruments open-hardware designs into fast (10s-100s MHz), deterministic, FPGA-based simulators that enable productive pre-silicon verification and performance validation. To model I/O, FireSim includes synthesizeable and timing-accurate models for standard interfaces like DRAM, Ethernet, UART, and others. The use of the elastic public cloud enable FireSim to scale simulations up to thousands of nodes. In order to use FireSim, the repository must be cloned and executed on AWS instances. See *FireSim* for more information.

## Prototyping

**FPGA Prototyping** FPGA prototyping is supported in Chipyard using SiFive's fpga-shells. Some examples of FPGAs supported are the Xilinx Arty 35T and VCU118 boards. For a fast and deterministic simulation with plenty of debugging tools, please consider using the *FireSim* platform. See *Prototyping Flow* for more information on FPGA prototypes.

## VLSI

Hammer Hammer is a VLSI flow designed to provide a layer of abstraction between general physical design concepts to vendor-specific EDA tool commands. The HAMMER flow provide automated scripts which generate relevant tool commands based on a higher level description of physical design constraints. The Hammer flow also allows for re-use of process technology knowledge by enabling the construction of process-technology-specific plugins, which describe particular constraints relating to that process technology (obsolete standard cells, metal layer routing constraints, etc.). The Hammer flow requires access to proprietary EDA tools and process technology libraries. See *Core Hammer* for more information.

## 2.1.2 Development Ecosystem

## **Chipyard Approach**

The trend towards agile hardware design and evaluation provides an ecosystem of debugging and implementation tools, that make it easier for computer architecture researchers to develop novel concepts. Chipyard hopes to build on this prior work in order to create a singular location to which multiple projects within the Berkeley Architecture Research can coexist and be used together. Chipyard aims to be the "one-stop shop" for creating and testing your own unique System on a Chip (SoC).

## **Chisel/FIRRTL**

One of the tools to help create new RTL designs quickly is the Chisel Hardware Construction Language and the FIRRTL Compiler. Chisel is an embedded language within Scala that provides a set of libraries to help hardware designers create highly parameterizable RTL. FIRRTL on the other hand is a compiler for hardware which allows the user to run FIRRTL passes that can do dead code elimination, circuit analysis, connectivity checks, and much more! These two tools in combination allow quick design space exploration and development of new RTL.

## **RTL Generators**

Within this repository, all of the Chisel RTL is written as generators. Generators are parametrized programs designed to generate RTL code based on configuration specifications. Generators can be used to generate Systems-on-Chip (SoCs) using a collection of system components organized in unique generator projects. Generators allow you to create a family of SoC designs instead of a single instance of a design!

## 2.1.3 Configs, Parameters, Mixins, and Everything In Between

A significant portion of generators in the Chipyard framework use the Rocket Chip parameter system. This parameter system enables for the flexible configuration of the SoC without invasive RTL changes. In order to use the parameter system correctly, we will use several terms and conventions:

## **Parameters**

It is important to note that a significant challenge with the Rocket parameter system is being able to identify the correct parameter to use, and the impact that parameter has on the overall system. We are still investigating methods to facilitate parameter exploration and discovery.

## Configs

A *config* is a collection of multiple generator parameters being set to specific values. Configs are additive, can override each other, and can be composed of other configs (sometimes referred to as config fragments). The naming convention for an additive config or config fragment is With<YourConfigName>, while the naming convention for a non-additive config will be <YourConfig>. Configs can take arguments which will in-turn set parameters in the design or reference other parameters in the design (see *Parameters*).

This example shows a basic config fragment class that takes in zero arguments and instead uses hardcoded values to set the RTL design parameters. In this example, MyAcceleratorConfig is a Scala case class that defines a set of variables that the generator can use when referencing the MyAcceleratorKey in the design.

```

class WithMyAcceleratorParams extends Config((site, here, up) => {

case BusWidthBits => 128

case MyAcceleratorKey =>

MyAcceleratorConfig(

rows = 2,

rowBits = 64,

columns = 16,

hartId = 1,

someLength = 256)

})

```

This next example shows a "higher-level" additive config fragment that uses prior parameters that were set to derive other parameters.

```

class WithMyMoreComplexAcceleratorConfig extends Config((site, here, up) => {

case BusWidthBits => 128

case MyAcceleratorKey =>

MyAcceleratorConfig(

Rows = 2,

rowBits = site(SystemBusKey).beatBits,

hartId = up(RocketTilesKey, site).length)

})

```

The following example shows a non-additive config that combines or "assembles" the prior two config fragments using ++. The additive config fragments are applied from the right to left in the list (or bottom to top in the example). Thus, the order of the parameters being set will first start with the DefaultExampleConfig, then WithMyAcceleratorParams, then WithMyMoreComplexAcceleratorConfig.

```

class SomeAdditiveConfig extends Config(

new WithMyMoreComplexAcceleratorConfig ++

new WithMyAcceleratorParams ++

new DefaultExampleConfig

```

The site, here, and up objects in WithMyMoreComplexAcceleratorConfig are maps from configuration keys to their definitions. The site map gives you the definitions as seen from the root of the configuration hierarchy (in this example, SomeAdditiveConfig). The here map gives the definitions as seen at the current level of the hierarchy (i.e. in WithMyMoreComplexAcceleratorConfig itself). The up map gives the definitions as seen from the next level up from the current (i.e. from WithMyAcceleratorParams).

## Cake Pattern / Mixin

A cake pattern or mixin is a Scala programming pattern, which enable "mixing" of multiple traits or interface definitions (sometimes referred to as dependency injection). It is used in the Rocket Chip SoC library and Chipyard framework in merging multiple system components and IO interfaces into a large system component.

This example shows the Chipyard default top that composes multiple traits together into a fully-featured SoC with many optional components.

```

class DigitalTop(implicit p: Parameters) extends ChipyardSystem

with testchipip.CanHaveTraceIO // Enables optionally adding trace IO

with testchipip.CanHaveBackingScratchpad // Enables optionally adding a backing,

\hookrightarrow scratchpad

with testchipip.CanHavePeripheryBlockDevice // Enables optionally adding the block.

→device

with testchipip.CanHavePeripheryTLSerial // Enables optionally adding the backing.

← memory and serial adapter

with sifive.blocks.devices.uart.HasPeripheryUART // Enables optionally adding the_

⇔sifive UART

with sifive.blocks.devices.gpio.HasPeripheryGPIO // Enables optionally adding the,

⇔sifive GPIOs

with sifive.blocks.devices.spi.HasPeripherySPIFlash // Enables optionally adding.

→the sifive SPI flash controller

with sifive.blocks.devices.spi.HasPeripherySPI // Enables optionally adding the.

⇔sifive SPI port

with icenet.CanHavePeripheryIceNIC // Enables optionally adding the IceNIC for_

→FireSim

with chipyard.example.CanHavePeripheryInitZero // Enables optionally adding the_

→initzero example widget

with chipyard.example.CanHavePeripheryGCD // Enables optionally adding the GCD_

→example widget

(continues on next page)

```

#### (continued from previous page)

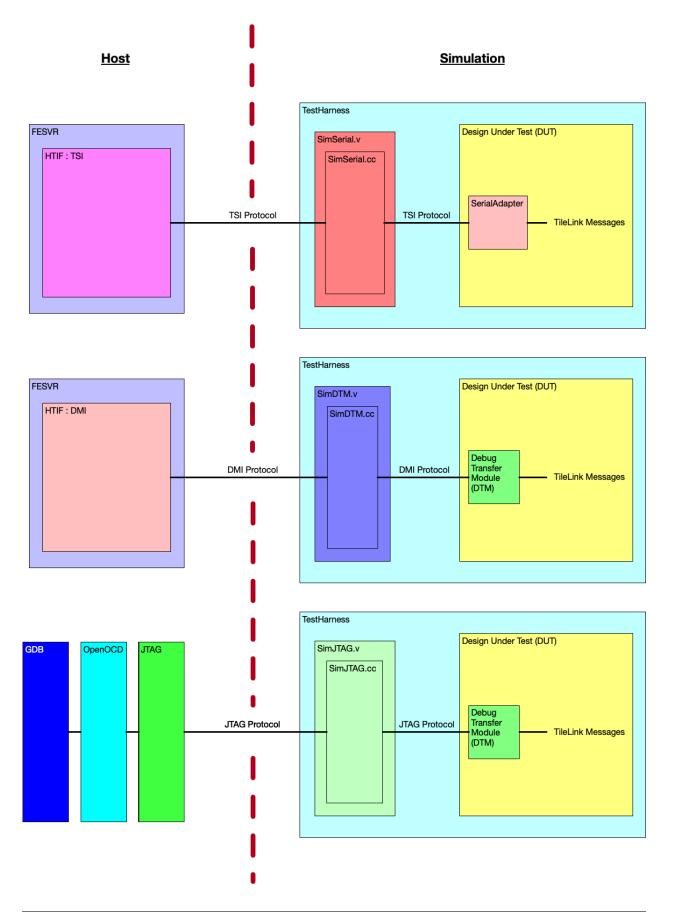

There are two "cakes" or mixins here. One for the lazy module (ex. CanHavePeripherySerial) and one for the lazy module implementation (ex. CanHavePeripherySerialModuleImp where Imp refers to implementation). The lazy module defines all the logical connections between generators and exchanges configuration information among them, while the lazy module implementation performs the actual Chisel RTL elaboration.

In the DigitalTop example class, the "outer" DigitalTop instantiates the "inner" DigitalTopModule as a lazy module implementation. This delays immediate elaboration of the module until all logical connections are determined and all configuration information is exchanged. The System outer base class, as well as the CanHavePeriphery<X> outer traits contain code to perform high-level logical connections. For example, the CanHavePeripherySerial outer trait contains code to optionally lazily instantiate the SerialAdapter, and connect the SerialAdapter's TileLink node to the Front bus.

The ModuleImp classes and traits perform elaboration of real RTL. For example, the CanHavePeripherySerialModuleImp trait optionally physically connects the SerialAdapter module, and instantiates queues.

In the test harness, the SoC is elaborated with val dut = p(BuildTop)(p).

After elaboration, the system submodule of ChipTop will be a DigitalTop module, which contains a SerialAdapter module (among others), if the config specified for that block to be instantiated.

From a high level, classes which extend LazyModule *must* reference their module implementation through lazy val module, and they *may* optionally reference other lazy modules (which will elaborate as child modules in the module hierarchy). The "inner" modules contain the implementation for the module, and may instantiate other normal modules OR lazy modules (for nested Diplomacy graphs, for example).

The naming convention for an additive mixin or trait is CanHave<YourMixin>. This is shown in the Top class where things such as CanHavePeripherySerial connect a RTL component to a bus and expose signals to the top-level.

## **Additional References**

Another description of traits/mixins and config fragments is given in *Keys, Traits, and Configs*. Additionally, a brief explanation of some of these topics (with slightly different naming) is given in the following video: https://www.youtube.com/watch?v=Eko86PGEoDY.

Note: Chipyard uses the name "config fragments" over "config mixins" to avoid confusion between a mixin applying

to a config or to the system Top (even though both are technically Scala mixins).

## 2.1.4 Initial Repository Setup

#### **Requirements**

Chipyard is developed and tested on Linux-based systems.

**Warning:** It is possible to use this on macOS or other BSD-based systems, although GNU tools will need to be installed; it is also recommended to install the RISC-V toolchain from brew.

Warning: Working under Windows is not recommended.

In CentOS-based platforms, we recommend installing the following dependencies:

```

#!/bin/bash

set -ex

sudo yum groupinstall -y "Development tools"

sudo yum install -y gmp-devel mpfr-devel libmpc-devel zlib-devel vim git java java-

⇔devel

curl https://bintray.com/sbt/rpm/rpm | sudo tee /etc/yum.repos.d/bintray-sbt-rpm.repo

sudo yum install -y sbt texinfo gengetopt

sudo yum install -y expat-devel libusb1-devel ncurses-devel cmake

→ "perl(ExtUtils::MakeMaker)"

# deps for poky

sudo yum install -y python36 patch diffstat texi2html texinfo subversion chrpath git.

⇔wget

# deps for gemu

sudo yum install -y gtk3-devel

# deps for firemarshal

sudo yum install -y python36-pip python36-devel rsync libguestfs-tools makeinfo expat_

⇔ctaqs

# Install GNU make 4.x (needed to cross-compile glibc 2.28+)

sudo yum install -y centos-release-scl

sudo yum install -y devtoolset-8-make

# install DTC

sudo yum install -y dtc

# install verilator

git clone http://git.veripool.org/git/verilator

cd verilator

git checkout v4.034

autoconf && ./configure && make -j16 && sudo make install

```

In Ubuntu/Debian-based platforms (Ubuntu), we recommend installing the following dependencies:

#!/bin/bash

set -ex

(continues on next page)

(continued from previous page)

```

sudo apt-get install -y build-essential bison flex

sudo apt-get install -y libgmp-dev libmpfr-dev libmpc-dev zliblg-dev vim git default-

⇒jdk default-jre

# install sbt: https://www.scala-sbt.org/release/docs/Installing-sbt-on-Linux.html

echo "deb https://dl.bintray.com/sbt/debian /" | sudo tee -a /etc/apt/sources.list.d/

⇔sbt.list

curl -sL "https://keyserver.ubuntu.com/pks/lookup?op=get&

→search=0x2EE0EA64E40A89B84B2DF73499E82A75642AC823" | sudo apt-key add

sudo apt-get update

sudo apt-get install -y sbt

sudo apt-get install -y texinfo gengetopt

sudo apt-get install -y libexpat1-dev libusb-dev libncurses5-dev cmake

# deps for poky

sudo apt-get install -y python3.6 patch diffstat texi2html texinfo subversion chrpath_

⇔git wget

# deps for qemu

sudo apt-get install -y libgtk-3-dev gettext

# deps for firemarshal

sudo apt-get install -y python3-pip python3.6-dev rsync libguestfs-tools expat ctags

# install DTC

sudo apt-get install -y device-tree-compiler

# install verilator

git clone http://git.veripool.org/git/verilator

cd verilator

git checkout v4.034

autoconf && ./configure && make -j$(nproc) && sudo make install

```

**Note:** When running on an Amazon Web Services EC2 FPGA-development instance (for FireSim), FireSim includes a machine setup script that will install all of the aforementioned dependencies (and some additional ones).

## Setting up the Chipyard Repo

Start by fetching Chipyard's sources. Run:

```

git clone https://github.com/ucb-bar/chipyard.git

cd chipyard

./scripts/init-submodules-no-riscv-tools.sh

```

This will initialize and checkout all of the necessary git submodules.

When updating Chipyard to a new version, you will also want to rerun this script to update the submodules. Using git directly will try to initialize all submodules; this is not recommended unless you expressly desire this behavior.

## **Building a Toolchain**

The *toolchains* directory contains toolchains that include a cross-compiler toolchain, frontend server, and proxy kernel, which you will need in order to compile code to RISC-V instructions and run them on your design. Currently there are two toolchains, one for normal RISC-V programs, and another for Hwacha (esp-tools). For custom installations, Each tool within the toolchains contains individual installation procedures within its README file. To get a basic installation (which is the only thing needed for most Chipyard use-cases), just the following steps are necessary. This

will take about 20-30 minutes. You can expedite the process by setting a make environment variable to use parallel cores: export MAKEFLAGS=-j8.

./scripts/build-toolchains.sh riscv-tools # for a normal risc-v toolchain

**Note:** If you are planning to use the Hwacha vector unit, or other RoCC-based accelerators, you should build the esp-tools toolchain by adding the esp-tools argument to the script above. If you are running on an Amazon Web Services EC2 instance, intending to use FireSim, you can also use the --ec2fast flag for an expedited installation of a pre-compiled toolchain.

Once the script is run, a env.sh file is emitted that sets the PATH, RISCV, and LD\_LIBRARY\_PATH environment variables. You can put this in your .bashrc or equivalent environment setup file to get the proper variables, or directly include it in your current environment:

source ./env.sh

These variables need to be set for the make system to work properly.

## What's Next?

This depends on what you are planning to do with Chipyard.

- If you intend to run a simulation of one of the vanilla Chipyard examples, go to *Software RTL Simulation* and follow the instructions.

- If you intend to run a simulation of a custom Chipyard SoC Configuration, go to *Simulating A Custom Project* and follow the instructions.

- If you intend to run a full-system FireSim simulation, go to *FPGA-Accelerated Simulation* and follow the instructions.

- If you intend to add a new accelerator, go to Basic customization and follow the instructions.

- If you want to learn about the structure of Chipyard, go to Chipyard Components.

- If you intend to change the generators (BOOM, Rocket, etc) themselves, see Included RTL Generators.

- If you intend to run a tutorial VLSI flow using one of the Chipyard examples, go to *ASAP7 Tutorial* and follow the instructions.

- If you intend to build a chip using one of the vanilla Chipyard examples, go to *Building A Chip* and follow the instructions.

#### **Upgrading Chipyard Release Versions**

In order to upgrade between Chipyard versions, we recommend using a fresh clone of the repository (or your fork, with the new release merged into it).

Chipyard is a complex framework that depends on a mix of build systems and scripts. Specifically, it relies on git submodules, on sbt build files, and on custom written bash scripts and generated files. For this reason, upgrading between Chipyard versions is **not** as trivial as just running git submodule update -recursive. This will result in recursive cloning of large submodules that are not necessarily used within your specific Chipyard environments. Furthermore, it will not resolve the status of stale state generated files which may not be compatible between release versions.

If you are an advanced git user, an alternative approach to a fresh repository clone may be to run git clean -dfx, and then run the standard Chipyard setup sequence. This approach is dangerous, and **not-recommended** for users

who are not deeply familiar with git, since it "blows up" the repository state and removes all untracked and modified files without warning. Hence, if you were working on custom un-committed changes, you would lose them.

If you would still like to try to perform an in-place manual version upgrade (**not-recommended**), we recommend at least trying to resolve stale state in the following areas:

- Delete stale target directories generated by sbt.

- Delete jar collateral generated by FIRRTL (lib/firrtl.jar)

- Re-generate generated scripts and source files (for example, env.sh)

- Re-generating/deleting target software state (Linux kernel binaries, Linux images) within FireMarshal

This is by no means a comprehensive list of potential stale state within Chipyard. Hence, as mentioned earlier, the recommended method for a Chipyard version upgrade is a fresh clone (or a merge, and then a fresh clone).

## 2.2 Simulation

Chipyard supports two classes of simulation:

- 1. Software RTL simulation using commercial or open-source (Verilator) RTL simulators

- 2. FPGA-accelerated full-system simulation using FireSim

Software RTL simulators of Chipyard designs run at O(1 KHz), but compile quickly and provide full waveforms. Conversely, FPGA-accelerated simulators run at O(100 MHz), making them appropriate for booting an operating system and running a complete workload, but have multi-hour compile times and poorer debug visibility.

Click next to see how to run a simulation.

## 2.2.1 Software RTL Simulation

## Verilator (Open-Source)

Verilator is an open-source LGPL-Licensed simulator maintained by Veripool. The Chipyard framework can down-load, build, and execute simulations using Verilator.

## Synopsys VCS (License Required)

VCS is a commercial RTL simulator developed by Synopsys. It requires commercial licenses. The Chipyard framework can compile and execute simulations using VCS. VCS simulation will generally compile faster than Verilator simulations.

To run a VCS simulation, make sure that the VCS simulator is on your PATH.

## **Choice of Simulator**

First, we will start by entering the Verilator or VCS directory:

For an open-source Verilator simulation, enter the sims/verilator directory

```

# Enter Verilator directory

cd sims/verilator

```

For a proprietry VCS simulation, enter the sims/vcs directory

# Enter VCS directory

cd sims/vcs

#### Simulating The Default Example

To compile the example design, run make in the selected verilator or VCS directory. This will elaborate the RocketConfig in the example project.

**Note:** The elaboration of RocketConfig requires about 6.5 GB of main memory. Otherwise the process will fail with make: \*\*\* [firrtl\_temp] Error 137 which is most likely related to limited resources. Other configurations might require even more main memory.

An executable called simulator-chipyard-RocketConfig will be produced. This executable is a simulator that has been compiled based on the design that was built. You can then use this executable to run any compatible RV64 code. For instance, to run one of the riscv-tools assembly tests.

```

./simulator-chipyard-RocketConfig $RISCV/riscv64-unknown-elf/share/riscv-tests/isa/

→rv64ui-p-simple

```

**Note:** In a VCS simulator, the simulator name will be simv-chipyard-RocketConfig instead of simulator-chipyard-RocketConfig.

The makefiles have a run-binary rule that simplifies running the simulation executable. It adds many of the common command line options for you and redirects the output to a file.

Alternatively, we can run a pre-packaged suite of RISC-V assembly or benchmark tests, by adding the make target run-asm-tests or run-bmark-tests. For example:

```

make run-asm-tests

make run-bmark-tests

```

**Note:** Before running the pre-packaged suites, you must run the plain make command, since the elaboration command generates a Makefile fragment that contains the target for the pre-packaged test suites. Otherwise, you will likely encounter a Makefile target error.

#### **Makefile Variables and Commands**

You can get a list of useful Makefile variables and commands available from the Verilator or VCS directories. simply run make help:

```

# Enter Verilator directory

cd sims/verilator

make help

# Enter VCS directory

```

(continues on next page)

(continued from previous page)

```

cd sims/vcs

make help

```

## **Simulating A Custom Project**

If you later create your own project, you can use environment variables to build an alternate configuration.

In order to construct the simulator with our custom design, we run the following command within the simulator directory:

```

make SBT_PROJECT=... MODEL=... VLOG_MODEL=... MODEL_PACKAGE=... CONFIG_... CONFIG_

↔PACKAGE=... GENERATOR_PACKAGE=... TB=... TOP=...

```

Each of these make variables correspond to a particular part of the design/codebase and are needed so that the make system can correctly build and make a RTL simulation.

The SBT\_PROJECT is the build.sbt project that holds all of the source files and that will be run during the RTL build.

The MODEL and VLOG\_MODEL are the top-level class names of the design. Normally, these are the same, but in some cases these can differ (if the Chisel class differs than what is emitted in the Verilog).

The MODEL\_PACKAGE is the Scala package (in the Scala code that says package ...) that holds the MODEL class.

The CONFIG is the name of the class used for the parameter config while the CONFIG\_PACKAGE is the Scala package it resides in.

The GENERATOR\_PACKAGE is the Scala package that holds the Generator class that elaborates the design.

The TB is the name of the Verilog wrapper that connects the TestHarness to VCS/Verilator for simulation.

Finally, the TOP variable is used to distinguish between the top-level of the design and the TestHarness in our system. For example, in the normal case, the MODEL variable specifies the TestHarness as the top-level of the design. However, the true top-level design, the SoC being simulated, is pointed to by the TOP variable. This separation allows the infrastructure to separate files based on the harness or the SoC top level.

Common configurations of all these variables are packaged using a SUB\_PROJECT make variable. Therefore, in order to simulate a simple Rocket-based example system we can use:

```

make SUB_PROJECT=yourproject

./simulator-<yourproject>-<yourconfig> ...

```

All make targets that can be applied to the default example, can also be applied to custom project using the custom environment variables. For example, the following code example will run the RISC-V assembly benchmark suite on the Hwacha subproject:

```

make SUB_PROJECT=hwacha run-asm-tests

```

Finally, in the generated-src/<...>-<package>-<config>/ directory resides all of the collateral and Verilog source files for the build/simulation. Specifically, the SoC top-level (TOP) Verilog file is denoted with \*. top.v while the TestHarness file is denoted with \*.harness.v.

#### **Fast Memory Loading**

The simulator loads the program binary over a simulated serial line. This can be quite slow if there is a lot of static data, so the simulator also allows data to be loaded from a file directly into the DRAM model.

make run-binary BINARY=test.riscv LOADMEM=testdata.hex LOADMEM\_ADDR=81000000

The . hex file should be a text file with a hexadecimal number on each line.

deadbeef 0123

Each line uses little-endian order, so this file would produce the bytes "ef be ad de 01 23". LOADMEM\_ADDR specifies which address in memory (in hexadecimal) to write the first byte to. The default is 0x81000000.

A special target that facilitates automatically generating a hex file for an entire elf RISC-V exectuable and then running the simulator with the appropriate flags is also available.

make run-binary-hex BINARY=test.riscv

#### **Generating Waveforms**

If you would like to extract waveforms from the simulation, run the command make debug instead of just make.

For a Verilator simulation, this will generate a vcd file (vcd is a standard waveform representation file format) that can be loaded to any common waveform viewer. An open-source vcd-capable waveform viewer is GTKWave.

For a VCS simulation, this will generate a vpd file (this is a proprietary waveform representation format used by Synopsys) that can be loaded to vpd-supported waveform viewers. If you have Synopsys licenses, we recommend using the DVE waveform viewer.

### **Additional Verilator Options**

When building the verilator simulator there are some additional options:

make VERILATOR\_THREADS=8 NUMACTL=1

The VERILATOR\_THREADS=<num> option enables the compiled Verilator simulator to use <num> parallel threads. On a multi-socket machine, you will want to make sure all threads are on the same socket by using NUMACTL=1 to enable numactl. By enabling this, you will use Chipyard's numa\_prefix wrapper, which is a simple wrapper around numactl that runs your verilated simulator like this: \$(numa\_prefix) ./simulator-<name> <simulator-args>. Note that both these flags are mutually exclusive, you can use either independently (though it makes sense to use NUMACTL just with VERILATOR\_THREADS=8 during a Verilator simulation).

## 2.2.2 FPGA-Accelerated Simulation

## **FireSim**

FireSim is an open-source cycle-accurate FPGA-accelerated full-system hardware simulation platform that runs on cloud FPGAs (Amazon EC2 F1). FireSim allows RTL-level simulation at orders-of-magnitude faster speeds than software RTL simulators. FireSim also provides additional device models to allow full-system simulation, including memory models and network models.

FireSim currently supports running only on Amazon EC2 F1 FPGA-enabled virtual instances. In order to simulate your Chipyard design using FireSim, if you have not already, follow the initial EC2 setup instructions as detailed in the FireSim documentation. Then clone Chipyard onto your FireSim manager instance, and setup your Chipyard repository as you would normally.

Next, initalize FireSim as a library in Chipyard by running:

```

# At the root of your chipyard repo

./scripts/firesim-setup.sh --fast

```

firesim-setup.sh initializes additional submodules and then invokes firesim's build-setup.sh script adding --library to properly initialize FireSim as a library submodule in chipyard. You may run ./sims/ firesim/build-setup.sh --help to see more options.

Finally, source the following environment at the root of the firesim directory:

```

cd sims/firesim

# (Recommended) The default manager environment (includes env.sh)

source sourceme-f1-manager.sh

```

Note: Every time you want to use FireSim with a fresh shell, you must source this sourceme-fl-manager.sh

At this point you're ready to use FireSim with Chipyard. If you're not already familiar with FireSim, please return to the FireSim Docs, and proceed with the rest of the tutorial.

## **Running your Design in FireSim**

Converting a Chipyard config (one in chipyard/src/main/scala to run in FireSim is simple, and can be done either through the traditional configuration system or through FireSim's build-recipes scheme.

A FireSim simulation requires 3 additional config fragments:

- WithFireSimConfigTweaks modifies your design to better fit the FireSim usage model. This is composed of multiple smaller config fragments. For example, the removal of clock-gating (using the WithoutClockGating config fragment) which is required for correct functioning of the compiler. This config fragment also includes other config fragments such as the inclusion of UART in the design, which although may technically be optional, is *strongly* recommended.

- WithDefaultMemModel provides a default configuration for FASED memory models in the FireSim simulation. See the FireSim documentation for details. This config fragment is currently included by default within WithFireSimConfigTweaks, so it isn't necessary to add in separately, but it is required if you choose not to use WithFireSimConfigTweaks.

- WithDefaultFireSimBridges sets the IOBinders key to use FireSim's Bridge system, which can drive target IOs with software bridge models running on the simulation host. See the FireSim documentation for details.

The simplest method to add this config fragments to your custom Chipyard config is through FireSim's build recipe scheme. After your FireSim environment is setup, you will define your custom build recipe in sims/firesim/deploy/deploy/config\_build\_recipes.ini. By prepending the FireSim config fragments (separated by \_) to your Chipyard configuration, these config fragments will be added to your custom configuration as if they were listed in a custom Chisel config class definition. For example, if you would like to convert the Chipyard LargeBoomConfig to a FireSim simulation with a DDR3 memory model, the appropriate FireSim TARGET\_CONFIG would be DDR3FRFCFSLLC4MB\_WithDefaultFireSimBridges\_WithFireSimConfigTweaks\_chipyard. LargeBoomConfig. Note that the FireSim config fragments are part of the firesim.firesim scala package

and therefore there do not need to be prefixed with the full package name as opposed to the Chipyard config fragments which need to be prefixed with the chipyard package name.

An alternative method to prepending the FireSim config fragments in the FireSim build recipe is to create a new "permanent" FireChip custom configuration, which includes the FireSim config fragments. We are using the same target (top) RTL, and only need to specify a new set of connection behaviors for the IOs of that module. Simply

create a matching config within generators/firechip/src/main/scala/TargetConfigs that inherits your config defined in chipyard.

```

class FireSimRocketConfig extends Config(

new WithDefaultFireSimBridges ++

new WithDefaultMemModel ++

new WithFireSimConfigTweaks ++

new chipyard.RocketConfig)

```

While this option seems to require the maintenance of additional configuration code, it has the benefit of allowing for the inclusion of more complex config fragments which also accept custom arguments (for example, WithDefaultMemModel can take an optional argument")

## 2.3 Included RTL Generators

A Generator can be thought of as a generalized RTL design, written using a mix of meta-programming and standard RTL. This type of meta-programming is enabled by the Chisel hardware description language (see *Chisel*). A standard RTL design is essentially just a single instance of a design coming from a generator. However, by using meta-programming and parameter systems, generators can allow for integration of complex hardware designs in automated ways. The following pages introduce the generators integrated with the Chipyard framework.

Chipyard bundles the source code for the generators, under the generators/ directory. It builds them from source each time (although the build system will cache results if they have not changed), so changes to the generators themselves will automatically be used when building with Chipyard and propagate to software simulation, FPGA-accelerated simulation, and VLSI flows.

## 2.3.1 Rocket Chip

Rocket Chip generator is an SoC generator developed at Berkeley and now supported by SiFive. Chipyard uses the Rocket Chip generator as the basis for producing a RISC-V SoC.

*Rocket Chip* is distinct from *Rocket core*, the in-order RISC-V CPU generator. Rocket Chip includes many parts of the SoC besides the CPU. Though Rocket Chip uses Rocket core CPUs by default, it can also be configured to use the BOOM out-of-order core generator or some other custom CPU generator instead.

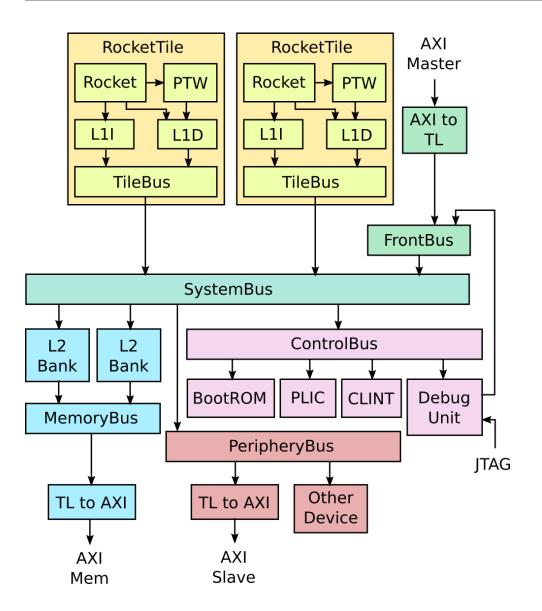

A detailed diagram of a typical Rocket Chip system is shown below.

## Tiles

The diagram shows a dual-core Rocket system. Each Rocket core is grouped with a page-table walker, L1 instruction cache, and L1 data cache into a RocketTile.

The Rocket core can also be swapped for a BOOM core. Each tile can also be configured with a RoCC accelerator that connects to the core as a coprocessor.

## **Memory System**

The tiles connect to the SystemBus, which connect it to the L2 cache banks. The L2 cache banks then connect to the MemoryBus, which connects to the DRAM controller through a TileLink to AXI converter.

To learn more about the memory hierarchy, see Memory Hierarchy.

## MMIO

For MMIO peripherals, the SystemBus connects to the ControlBus and PeripheryBus.

The ControlBus attaches standard peripherals like the BootROM, the Platform-Level Interrupt Controller (PLIC), the core-local interrupts (CLINT), and the Debug Unit.

The BootROM contains the first stage bootloader, the first instructions to run when the system comes out of reset. It also contains the Device Tree, which is used by Linux to determine what other peripherals are attached.

The PLIC aggregates and masks device interrupts and external interrupts.

The core-local interrupts include software interrupts and timer interrupts for each CPU.

The Debug Unit is used to control the chip externally. It can be used to load data and instructions to memory or pull data from memory. It can be controlled through a custom DMI or standard JTAG protocol.

The PeripheryBus attaches additional peripherals like the NIC and Block Device. It can also optionally expose an external AXI4 port, which can be attached to vendor-supplied AXI4 IP.

To learn more about adding MMIO peripherals, check out the MMIO Peripherals section.

## DMA

You can also add DMA devices that read and write directly from the memory system. These are attached to the FrontendBus. The FrontendBus can also connect vendor-supplied AXI4 DMA devices through an AXI4 to TileLink converter.

To learn more about adding DMA devices, see the Adding a DMA Device section.

## 2.3.2 Rocket Core

Rocket is a 5-stage in-order scalar processor core generator, originally developed at UC Berkeley and currently supported by SiFive. The *Rocket core* is used as a component within the *Rocket Chip SoC generator*. A Rocket core combined with L1 caches (data and instruction caches) form a *Rocket tile*. The *Rocket tile* is the replicable component of the *Rocket Chip SoC generator*.

The Rocket core supports the open-source RV64GC RISC-V instruction set and is written in the Chisel hardware construction language. It has an MMU that supports page-based virtual memory, a non-blocking data cache, and a front-end with branch prediction. Branch prediction is configurable and provided by a branch target buffer (BTB), branch history table (BHT), and a return address stack (RAS). For floating-point, Rocket makes use of Berkeley's Chisel implementations of floating-point units. Rocket also supports the RISC-V machine, supervisor, and user privilege levels. A number of parameters are exposed, including the optional support of some ISA extensions (M, A, F, D), the number of floating-point pipeline stages, and the cache and TLB sizes.

For more information, please refer to the GitHub repository, technical report or to this Chisel Community Conference video.

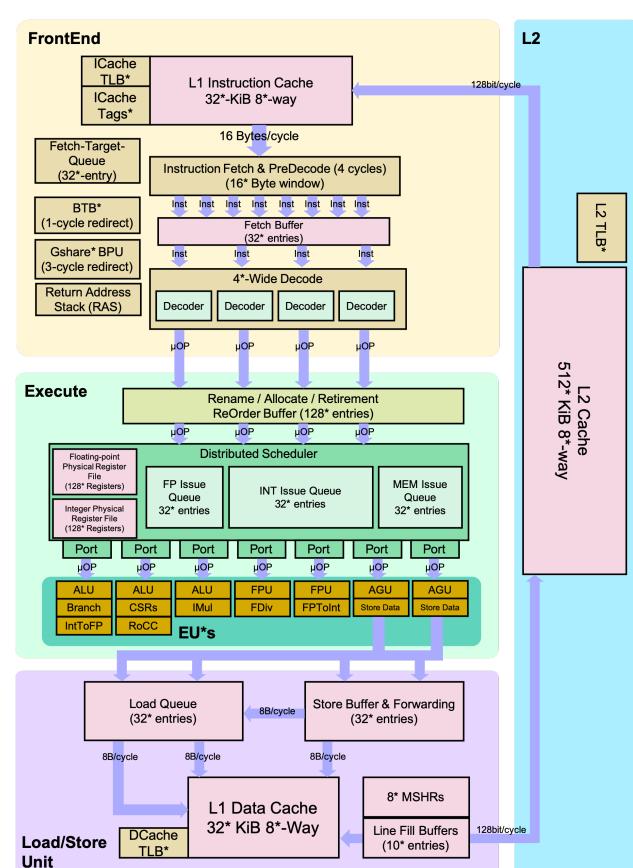

## 2.3.3 Berkeley Out-of-Order Machine (BOOM)

2.3. Included RTL Generators

The Berkeley Out-of-Order Machine (BOOM) is a synthesizable and parameterizable open source RV64GC RISC-V core written in the Chisel hardware construction language. It serves as a drop-in replacement to the Rocket core given by Rocket Chip (replaces the RocketTile with a BoomTile). BOOM is heavily inspired by the MIPS R10k and the Alpha 21264 out-of-order processors. Like the R10k and the 21264, BOOM is a unified physical register file design (also known as "explicit register renaming"). Conceptually, BOOM is broken up into 10 stages: Fetch, Decode, Register Rename, Dispatch, Issue, Register Read, Execute, Memory, Writeback and Commit. However, many of those stages are combined in the current implementation, yielding seven stages: Fetch, Decode/Rename, Rename/Dispatch, Issue/RegisterRead, Execute, Memory and Writeback (Commit occurs asynchronously, so it is not counted as part of the "pipeline").

Additional information about the BOOM micro-architecture can be found in the BOOM documentation pages.

## 2.3.4 Hwacha

The Hwacha project is developing a new vector architecture for future computer systems that are constrained in their power and energy consumption. The Hwacha project is inspired by traditional vector machines from the 70s and 80s, and lessons learned from our previous vector-thread architectures such as Scale and Maven The Hwacha project includes the Hwacha microarchitecture generator, as well as the XHwacha non-standard RISC-V extension. Hwacha does not implement the RISC-V standard vector extension proposal.

For more information on the Hwacha project, please visit the Hwacha website.

To add the Hwacha vector unit to an SoC, you should add the hwacha.DefaultHwachaConfig config fragment to the SoC configurations. The Hwacha vector unit uses the RoCC port of a Rocket or BOOM *tile*, and by default connects to the memory system through the *System Bus* (i.e., directly to the L2 cache).

To change the configuration of the Hwacha vector unit, you can write a custom configuration to replace the DefaultHwachaConfig. You can view the DefaultHwachaConfig under generators/hwacha/src/main/scala/configs.scala to see the possible configuration parameters.

Since Hwacha implements a non-standard RISC-V extension, it requires a unique software toolchain to be able to compile and assemble its vector instructions. To install the Hwacha toolchain, run the ./scripts/build-toolchains.sh esp-tools command within the root Chipyard directory. This may take a while, and it will install the esp-tools-install directory within your Chipyard root directory. esp-tools is a fork of riscv-tools (formerly a collection of relevant software RISC-V tools) that was enhanced with additional non-standard vector instructions. However, due to the upstreaming of the equivalent RISC-V toolchains, esp-tools may not be up-to-date with the latest mainline version of the tools included in it.

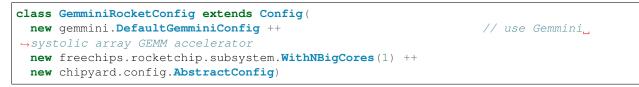

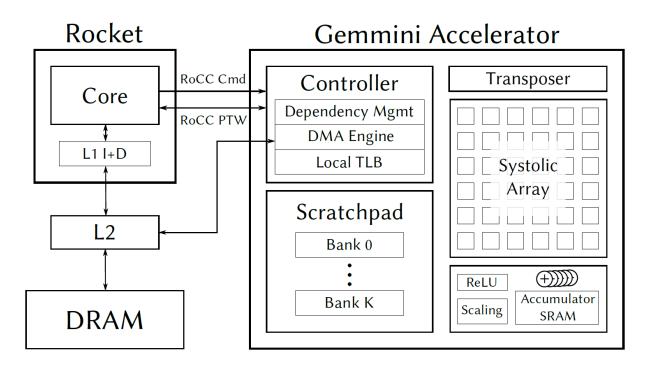

## 2.3.5 Gemmini

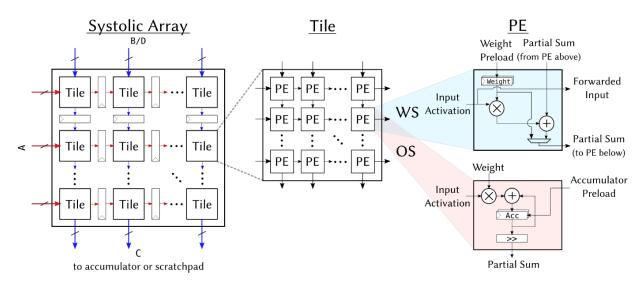

The Gemmini project is developing a systolic-array based matrix multiplication unit generator for the investigation of software/hardware implications of such integrated SoC accelerators. It is inspired by recent trends in machine learning accelerators for edge and mobile SoCs.

Gemmini is implemented as a RoCC accelerator with non-standard RISC-V custom instructions. The Gemmini unit uses the RoCC port of a Rocket or BOOM *tile*, and by default connects to the memory system through the System Bus (i.e., directly to the L2 cache).

To add a Gemmini unit to an SoC, you should add the gemmini.DefaultGemminiConfig config fragment to the SoC configurations. To change the configuration of the Gemmini accelerator unit, you can write a custom configuration to replace the DefaultGemminiConfig, which you can view under generators/gemmini/src/main/scala/configs.scala to see the possible configuration parameters.

The example Chipyard config includes the following example SoC configuration which includes Gemmini:

To build a simulation of this example Chipyard config, run the following commands:

```

cd sims/verilator # or "cd sims/vcs"

make CONFIG=GemminiRocketConfig

```

## **Generator Parameters**

Major parameters of interest include:

• Systolic array dimensions (tileRows, tileColumns, meshRows, meshColumns): The systolic array is composed of a 2-level hierarchy, in which each tile is fully combinational, while a mesh of tiles has pipeline registers between each tile.

- Dataflow parameters (dataflow): Determine whether the systolic array in Gemmini is output-stationary or weight-stationary, or whether it supports both dataflows so that programmers may choose between them at runtime.

- Scratchpad and accumulator memory parameters (sp\_banks, sp\_capacity, acc\_capacity): Determine the properties of the Gemmini scratchpad memory: overall capacity of the scratchpad or accumulators (in KiB), and the number of banks the scratchpad is divided into.

- Type parameters (inputType, outputType, accType): Determine the data-types flowing through different parts of a Gemmini accelerator. For example, inputType may be an 8-bit fixed-point number, while accType, which determines the type of partial accumulations in a matrix multiplication, may be a 32-bit integer. outputType only determines the type of the data passed between two processing elements (PEs); for example, an 8-bit multiplication may produce a 16-bit result which must be shared between PEs in a systolic array. If your datatype is a floating-point number, then you might also want to change the pe\_latency parameter, which specifies how many shift registers to add inside the PEs. This might be necessary if your datatype cannot complete a multiply-accumulate operation within a single cycle.

- Access-execute queue parameters (ld\_queue\_length, st\_queue\_length, ex\_queue\_length, rob\_entries): To implement access-execute decoupling, a Gemmini accelerator has a load instruction queue, a store instruction queue, and an execute instruction queue. The relative sizes of these queue determine the level of access-execute decoupling. Gemmini also implements a reorder buffer (ROB) the number of entries in the ROB determines possible dependency management limitations.

- DMA parameters (dma\_maxbytes, dma\_buswidth, mem\_pipeline): Gemmini implements a DMA to move data from main memory to the Gemmini scratchpad, and from the Gemmini accumulators to main memory. The size of these DMA transactions is determined by the DMA parameters. These DMA parameters are tightly coupled with Rocket Chip SoC system parameters: in particular dma\_buswidth is associated with the SystemBusKey beatBytes parameter, and dma\_maxbytes is associated with cacheblockbytes Rocket Chip parameters.

There are also optional features, which can be either enabled or left out of Gemmini at elaboration-time. For example:

Scaling during "move-in" operations (mvin\_scale\_args, mvin\_scale\_acc\_args): When data is being moved in from DRAM or main memory into Gemmini's local scratchpad memory, it can optionally be multiplied by a scaling factor. These parameters specify what the datatype of the scaling factor is, and how the scaling is actually done. If these are set to None, then this optional feature will be disabled at elaboration time. If both the scratchpad inputs are accumulator inputs are to be scaled in the same say, then the mvin\_scale\_shared parameter can be set to true so that the multipliers and functional units are shared.

### **Gemmini Software**

The Gemmini non-standard ISA extension is specified in the Gemmini repository. The ISA includes configuration instructions, data movement instructions (from main memory to the Gemmini scratchpad, and from the Gemmini accumulators to main memory), and matrix multiplication execution instructions.

Since Gemmini instructions are not exposed through the GNU binutils assembler, several C macros are provided in order to construct the instruction encodings to call these instructions.

The Gemmini generator includes a C matrix multiplication library which wraps the calls to the custom Gemmini instructions. The software directory of the generator (within the generator repository in generators/gemmini/ software) includes the aforementioned library and macros, as well as bare-metal tests, and some FireMarshal workloads to run the tests in a Linux environment. In particular, the matrix multiplication C library can be found in the generators/gemmini/software/gemmini-rocc-tests/include/gemmini.h file.

The Gemmini generator generates a C header file based on the generator parameters. This header files gets compiled together with the matrix multiplication library to tune library performance. The generated header file can be found under generators/gemmini/software/gemmini-rocc-tests/include/gemmini\_params.h

Gemmini can also be used to run ONNX-specified neural-networks through a port of Microsoft's ONNX-Runtime framework. The port is included as the onnxruntime-riscv repository submoduled in the *software* directory. The port is under development, and usage documentation can be found within its repository.

#### **Build and Run Gemmini Tests**

#### To build Gemmini tests:

```

cd generators/gemmini/software/gemmini-rocc-tests/

./build.sh

```

Afterwards, the test binaries will be found in generators/gemmini/software/gemmini-rocc-tests/ build. Binaries whose names end in -baremetal are meant to be run in a bare-metal environment, while binaries whose names end in -linux are meant to run in a Linux environment. You can run the tests either on a cycle-accurate RTL simulator, or on a (much faster) functional ISA simulator called Spike.

The Gemmini generator implements a custom non-standard version of Spike. This implementation is found within the esp-tools Spike implementation, together with the Hwacha vector accelerator non-standard ISA-extension. In order to use this version of Spike, please make sure to build the esp-tools software toolchain, as described in *Building a Toolchain*.

In order to run Spike with the gemmini functional model, you will need to use the --extension=gemmini flag. For example:

spike --extension=gemmini <some/gemmini/baremetal/test>

Spike is built by default without a commit log. However, if you would like to add detailed functional log of gemmini operation to the spike model, you can rebuild spike manually (based on the instructions in the esp-tools/ riscv-isa-sim/README file), with the --enable-gemminicommitlog option added to the configure step.

## Alternative SoC Configs

The Gemmini generator includes additional alternative SoC configs (configs that are not in the Chipyard example project). If you would like to build one of these alternative SoC configurations which are defined in within the Gemmini project repository, you can run the following commands. These commands are similar to the one required

when building a simulation from the example project, but they specify that the location of the configs are in the Gemmini subproject, as opposed to the Chipyard example project:

```

cd sims/verilator # or "cd sims/vcs"

make CONFIG=GemminiAcceleratorConfig CONFIG_PACKAGE=gemmini MODEL_PACKAGE=freechips.

→rocketchip.system GENERATOR_PACKAGE=freechips.rocketchip.system_

→TOP=ExampleRocketSystem

```

## 2.3.6 IceNet

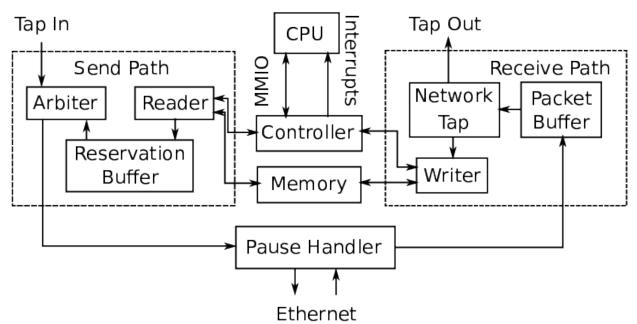

IceNet is a library of Chisel designs related to networking. The main component of IceNet is IceNIC, a network interface controller that is used primarily in FireSim for multi-node networked simulation. A diagram of IceNet's microarchitecture is shown below.

There are four basic parts of the NIC: the *Controller*, which takes requests from and sends responses to the CPU; the *Send Path*, which reads data from memory and sends it out to the network; the *Receive Path*, which receives data from the network and writes it to memory; and, optionally, the *Pause Handler*, which generates Ethernet pause frames for the purpose of flow control.

## Controller

The controller exposes a set of MMIO registers to the CPU. The device driver writes to registers to request that packets be sent or to provide memory locations to write received data to. Upon the completion of a send request or packet receive, the controller sends an interrupt to the CPU, which clears the completion by reading from another register.

## Send Path

The send path begins at the reader, which takes requests from the controller and reads the data from memory.

Since TileLink responses can come back out-of-order, we use a reservation queue to reorder responses so that the packet data can be sent out in the proper order.

The packet data then goes to an arbiter, which can arbitrate access to the outbound network interface between the NIC and one or more "tap in" interfaces, which come from other hardware modules that may want to send Ethernet packets. By default, there are no tap in interfaces, so the arbiter simply passes the output of the reservation buffer through.

## **Receive Path**

The receive path begins with the packet buffer, which buffers data coming in from the network. If there is insufficient space in the buffer, it will drop data at packet granularity to ensure that the NIC does not deliver incomplete packets.

From the packet buffer, the data can optionally go to a network tap, which examines the Ethernet header and select packets to be redirected from the NIC to external modules through one or more "tap out" interfaces. By default, there are no tap out interfaces, so the data will instead go directly to the writer, which writes the data to memory and then sends a completion to the controller.

## **Pause Handler**

IceNIC can be configured to have pause handler, which sits between the send and receive paths and the Ethernet interface. This module tracks the occupancy of the receive packet buffer. If it sees the buffer filling up, it will send an Ethernet pause frame out to the network to block further packets from being sent. If the NIC receives an Ethernet pause frame, the pause handler will block sending from the NIC.

## **Linux Driver**

The default Linux configuration provided by firesim-software contains an IceNet driver. If you launch a FireSim image that has IceNIC on it, the driver will automatically detect the device, and you will be able to use the full Linux networking stack in userspace.

## Configuration

To add IceNIC to your design, add HasPeripheryIceNIC to your lazy module and HasPeripheryIceNICModuleImp to the module implementation. If you are confused about the distinction between lazy module and module implementation, refer to *Cake Pattern / Mixin*.

Then add the WithIceNIC config fragment to your configuration. This will define NICKey, which IceNIC uses to determine its parameters. The config fragment takes two arguments. The inBufFlits argument is the number of 64-bit flits that the input packet buffer can hold and the usePauser argument determines whether or not the NIC will have a pause handler.

## 2.3.7 Test Chip IP

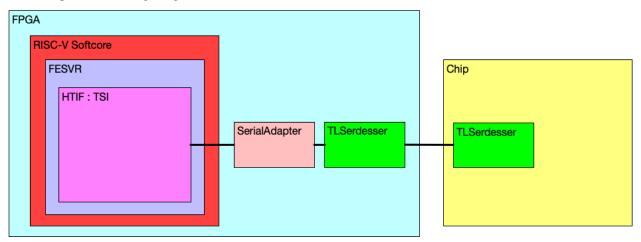

Chipyard includes a Test Chip IP library which provides various hardware widgets that may be useful when designing SoCs. This includes a *Serial Adapter*, *Block Device Controller*, *TileLink SERDES*, *TileLink Switcher*, *TileLink Ring Network*, and *UART Adapter*.

## **Serial Adapter**

The serial adapter is used by tethered test chips to communicate with the host processor. An instance of RISC-V frontend server running on the host CPU can send commands to the serial adapter to read and write data from the memory system. The frontend server uses this functionality to load the test program into memory and to poll for completion of the program. More information on this can be found in *Chipyard Boot Process*.

## **Block Device Controller**

The block device controller provides a generic interface for secondary storage. This device is primarily used in FireSim to interface with a block device software simulation model. The default Linux configuration in firesim-software

To add a block device to your design, add the WithBlockDevice config fragment to your configuration.

## **TileLink SERDES**

The TileLink SERDES in the Test Chip IP library allow TileLink memory requests to be serialized so that they can be carried off chip through a serial link. The five TileLink channels are multiplexed over two SERDES channels, one in each direction.

There are three different variants provided by the library, TLSerdes exposes a manager interface to the chip, tunnels A, C, and E channels on its outbound link, and tunnels B and D channels on its inbound link. TLDesser exposes a client interface to the chip, tunnels A, C, and E on its inbound link, and tunnels B and D on its outbound link. Finally, TLSerdesser exposes both client and manager interface to the chip and can tunnel all channels in both directions.

For an example of how to use the SERDES classes, take a look at the SerdesTest unit test in the Test Chip IP unit test suite.

## **TileLink Switcher**

The TileLink switcher is used when the chip has multiple possible memory interfaces and you would like to select which channels to map your memory requests to at boot time. It exposes a client node, multiple manager nodes, and a select signal. Depending on the setting of the select signal, requests from the client node will be directed to one of the manager nodes. The select signal must be set before any TileLink messages are sent and be kept stable throughout the remainder of operation. It is not safe to change the select signal once TileLink messages have begun sending.

For an example of how to use the switcher, take a look at the SwitcherTest unit test in the Test Chip IP unit tests.

## **TileLink Ring Network**

TestChipIP provides a TLRingNetwork generator that has a similar interface to the TLXbar provided by RocketChip, but uses ring networks internally rather than crossbars. This can be useful for chips with very wide TileLink networks (many cores and L2 banks) that can sacrifice cross-section bandwidth to relieve wire routing congestion. Documentation on how to use the ring network can be found in *The System Bus*. The implementation itself can be found here, and may serve as an example of how to implement your own TileLink network with a different topology.

#### **UART Adapter**

The UART Adapter is a device that lives in the TestHarness and connects to the UART port of the DUT to simulate communication over UART (ex. printing out to UART during Linux boot). In addition to working with stdin/stdout of the host, it is able to output a UART log to a particular file using +uartlog=<NAME\_OF\_FILE> during simulation.

By default, this UART Adapter is added to all systems within Chipyard by adding the WithUART and WithUARTAdapter configs.

#### **SPI Flash Model**

The SPI flash model is a device that models a simple SPI flash device. It currently only supports single read, quad read, single write, and quad write instructions. The memory is backed by a file which is provided using +spiflash#=<NAME\_OF\_FILE>, where # is the SPI flash ID (usually 0).

## 2.3.8 SiFive Generators

Chipyard includes several open-source generators developed and maintained by SiFive. These are currently organized within two submodules named sifive-blocks and sifive-cache.

#### **Last-Level Cache Generator**

sifive-cache includes last-level cache geneator. The Chipyard framework uses this last-level cache as an L2 cache. To use this L2 cache, you should add the freechips.rocketchip.subsystem. WithInclusiveCache config fragment to your SoC configuration. To learn more about configuring this L2 cache, please refer to the *Memory Hierarchy* section.

#### **Peripheral Devices**

sifive-blocks includes multiple peripheral device generators, such as UART, SPI, PWM, JTAG, GPIO and more.

These peripheral devices usually affect the memory map of the SoC, and its top-level IO as well. To integrate one of these devices in your SoC, you will need to define a custom config fragment with the approriate address for the device using the Rocket Chip parameter system. As an example, for a GPIO device you could add the following config fragment to set the GPIO address to 0x10012000. This address is the start address for the GPIO configuration registers.

```

class WithGPIO extends Config((site, here, up) => {

case PeripheryGPIOKey => Seq(

GPIOParams(address = 0x10012000, width = 4, includeIOF = false))

})

```

Additionally, if the device requires top-level IOs, you will need to define a config fragment to change the top-level configuration of your SoC. When adding a top-level IO, you should also be aware of whether it interacts with the test-harness.

This example instantiates a top-level module with include GPIO ports, and then ties-off the GPIO port inputs to 0 (false.B).

Finally, you add the relevant config fragment to the SoC config. For example:

```

class GPIORocketConfig extends Config(

new chipyard.config.WithGPIO ++ // add GPIOs to the_

→peripherybus

new freechips.rocketchip.subsystem.WithNBigCores(1) ++

new chipyard.config.AbstractConfig)

```

Some of the devices in sifive-blocks (such as GPIO) may already have pre-defined config fragments within the Chipyard example project. You may be able to use these config fragments directly, but you should be aware of their addresses within the SoC address map.

## 2.3.9 SHA3 RoCC Accelerator

The SHA3 accelerator is a basic RoCC accelerator for the SHA3 hashing algorithm. We like using SHA3 in Chipyard tutorial content because it is a self-contained, simple example of integrating a custom accelerator into Chipyard.

## Introduction

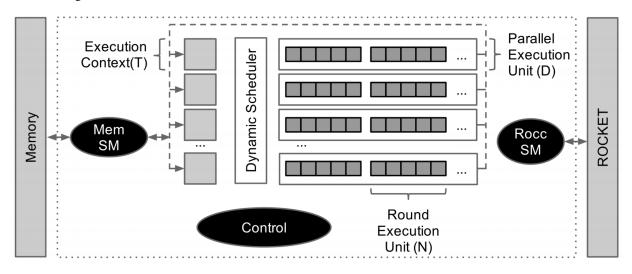

Secure hashing algorithms represent a class of hashing functions that provide four attributes: ease of hash computation, inability to generate the message from the hash (one-way property), inability to change the message and not the hash (weakly collision free property), and inability to find two messages with the same hash (strongly collision free property). The National Institute of Standards and Technology (NIST) recently held a competition for a new algorithm to be added to its set of Secure Hashing Algorithms (SHA). In 2012 the winner was determined to be the Keccak hashing function and a rough specification for SHA3 was established. The algorithm operates on variable length messages with a sponge function, and thus alternates between absorbing chunks of the message into a set of state bits and permuting the state. The absorbing is a simple bitwise XOR while the permutation is a more complex function composed of several operations,  $\chi$ ,  $\theta$ ,  $\rho$ ,  $\pi$ ,  $\iota$ , that all perform various bitwise operations, including rotations, parity calculations, XORs, etc. The Keccak hashing function is parameterized for different sizes of state and message chunks but for this accelerator we will only support the Keccak-256 variant with 1600 bits of state and 1088 bit message chunks. A diagram of the SHA3 accelerator is shown below.

## **Technical Details**

The accelerator is designed around three sub-systems, an interface with the processor, an interface with memory, and the actual hashing computation system. The interface with the processor is designed using the ROCC interface for coprocessors integrating with the RISC-V Rocket/BOOM processor. It includes the ability to transfer two 64 bit words to the co-processor, the request for a return value, and a small field for the function requested. The accelerator receives these requests using a ready/valid interface. The ROCC instruction is parsed and the needed information is stored into a execution context. The execution context contains the memory address of the message being hashed, the memory address to store the resulting hash in, the length of the message, and several other control fields.

Once the execution context is valid the memory subsystem then begins to fetch chunks of the message. The memory subsystem is fully decoupled from the other subsystems and maintains a single full round memory buffers. The accelerators memory interface can provide a maximum of one 64 bit word per cycle which corresponds to 17 requests needed to fill a buffer (the size is dictated by the SHA3 algorithm). Memory requests to fill these buffers are sent out as rapidly as the memory interface can handle, with a tag field set to allow the different memory buffers requests to be distinguished, as they may be returned out of order. Once the memory subsystem has filled a buffer the control unit

absorbs the buffer into the execution context, at which point the execution context is free to begin permutation, and the memory buffer is free to send more memory requests.

After the buffer is absorbed, the hashing computation subsystem begins the permutation operations. Once the message is fully hashed, the hash is written to memory with a simple state machine.

#### **Using a SHA3 Accelerator**

Since the SHA3 accelerator is designed as a RoCC accelerator, it can be mixed into a Rocket or BOOM core by overriding the BuildRoCC key. The config fragment is defined in the SHA3 generator. An example configuration highlighting the use of this config fragment is shown here:

```

class Sha3RocketConfig extends Config(

new sha3.WithSha3Accel ++ // add SHA3 rocc_

→accelerator

new freechips.rocketchip.subsystem.WithNBigCores(1) ++

new chipyard.config.AbstractConfig)

```

The SHA3 example baremetal and Linux tests are located in the SHA3 repository. Please refer to its README.md for more information on how to run/build the tests.

## 2.3.10 CVA6 Core

CVA6 (previously called Ariane) is a 6-stage in-order scalar processor core, originally developed at ETH-Zurich by F. Zaruba and L. Benini. The *CVA6 core* is wrapped in an *CVA6 tile* so it can be used as a component within the *Rocket Chip SoC generator*. The core by itself exposes an AXI interface, interrupt ports, and other misc. ports that are connected from within the tile to TileLink buses and other parameterization signals.

**Warning:** Since the core uses an AXI interface to connect to memory, it is highly recommended to use the core in a single-core setup (since AXI is a non-coherent memory interface).

While the core itself is not a generator, we expose the same parameterization that the CVA6 core provides (i.e. change branch prediction parameters).